UOMOP

Whole Processing using PhaseSplitter 본문

TestBench code

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

library work;

use work.mypackage.all;

entity whole_12week is

end entity;

architecture behavior of whole_12week is

component rbgen is

port(

nrst, clk : in std_logic;

rbit : out std_logic);

end component;

component clkgen is

port(

nrst, mclk : in std_logic;

clk8x, clk4x, clk2x, clk1x : out std_logic);

end component;

component s2p is

generic (prate : in integer);

port(

nrst, sclk, pclk, inbit : in std_logic;

outbits : out std_logic_vector((prate-1) downto 0));

end component;

component QAM16mapper is

port(

nrst, sclk : in std_logic;

inbits : in std_logic_vector(3 downto 0);

rdata : out std_logic_vector(5 downto 0);

idata : out std_logic_vector(5 downto 0));

end component;

component QAM16demapper is

port(

nrst, sclk : in std_logic;

rdata, idata : std_logic_vector(5 downto 0);

outbits : out std_logic_vector(3 downto 0));

end component;

component UpSample is

generic( UpRatio : integer := 4;

Dwidth : integer := 6);

port(

nrst, upclk : in std_logic;

rdin, idin : in std_logic_vector((Dwidth-1) downto 0);

rdout, idout : out std_logic_vector((Dwidth-1) downto 0));

end component;

component DnSample is

generic ( DnRatio : integer := 4;

Dwidth : integer := 10;

LatchTime : integer := 7);

port(

nrst, upclk, dnclk : in std_logic;

rdin, idin : in std_logic_vector((Dwidth-1) downto 0);

rdout, idout : out std_logic_vector((Dwidth-1) downto 0));

end component;

component psf65T is

port(

nrst : in std_logic;

clk : in std_logic;

PSFin: in std_logic_vector(9 downto 0);

PSFout : out std_logic_vector(9 downto 0));

end component;

component p2s is

generic(prate : in integer);

port(

nrst, sclk : in std_logic;

inbits : in std_logic_vector((prate-1) downto 0);

outbit : out std_logic);

end component;

component UpConv_NCO is

port(

nrst, clk : in std_logic;

omega : in std_logic_vector(7 downto 0);

base_r, base_i : in std_logic_vector(9 downto 0);

pass_r, pass_i : out std_logic_vector(9 downto 0));

end component;

component DnConv_NCO is

port(

nrst, clk : in std_logic;

omega : in std_logic_vector( 7 downto 0 );

pass_r, pass_i : in std_logic_vector( 9 downto 0 );

base_r, base_i : out std_logic_vector( 9 downto 0 ));

end component;

component PhaseSplitter is

port(

nrst, clk : in std_logic;

PS_Iin : in std_logic_vector(9 downto 0);

PS_Iout, PS_Qout : out std_logic_vector(9 downto 0));

end component;

signal nrst, mclk : std_logic;

signal clk8x, clk4x, clk2x, clk1x : std_logic;

signal rbit : std_logic;

signal s2pout : std_logic_vector(3 downto 0);

signal rmapout, imapout : std_logic_vector(5 downto 0);

signal rupout, iupout : std_logic_vector(5 downto 0);

signal rupout_0000, iupout_0000 : std_logic_vector(9 downto 0);

signal rpsfout1, ipsfout1 : std_logic_vector(9 downto 0);

signal upreal, upimag : std_logic_vector(9 downto 0);

signal r, i : std_logic_vector(9 downto 0);

signal rpsfout2, ipsfout2 : std_logic_vector(9 downto 0);

signal rdnout, idnout : std_logic_vector(9 downto 0);

signal rpsfout_final, ipsfout_final : std_logic_vector(5 downto 0);

signal ri_after_demap : std_logic_vector(3 downto 0);

signal p2sout : std_logic;

signal after_phase_r, after_phase_i : std_logic_vector(9 downto 0);

begin

iclkgen : clkgen port map(

nrst => nrst,

mclk => mclk,

clk8x => clk8x,

clk4x => clk4x,

clk2x => clk2x,

clk1x => clk1x);

irbgen : rbgen port map(

nrst => nrst,

clk => clk4x,

rbit => rbit);

is2p : s2p

generic map(prate => 4)

port map(

nrst => nrst,

sclk => clk4x,

pclk => clk1x,

inbit => rbit,

outbits => s2pout);

iqmap : QAM16mapper port map(

nrst => nrst,

sclk => clk1x,

inbits => s2pout,

rdata => rmapout,

idata => imapout);

iupsam : UpSample

generic map(UpRatio => 8,

Dwidth => 6)

port map(

nrst => nrst,

upclk => clk8x,

rdin => rmapout,

idin => imapout,

rdout => rupout,

idout => iupout);

rupout_0000 <= rupout & "0000";

iupout_0000 <= iupout & "0000";

ipsf65T_r_tx : psf65T port map(

nrst => nrst,

clk => clk8x,

PSFin => rupout_0000,

PSFout => rpsfout1);

ipsf65T_i_tx : psf65T port map(

nrst => nrst,

clk => clk8x,

PSFin => iupout_0000,

PSFout => ipsfout1);

iupconv : UpConv_NCO port map(

nrst => nrst,

clk => clk8x,

omega => "01000000",

base_r => rpsfout1,

base_i => ipsfout1,

pass_r => upreal,

pass_i => upimag);

iphasesplit : PhaseSplitter port map(

nrst => nrst,

clk => clk8x,

PS_Iin => upreal,

PS_Iout => after_phase_r,

PS_Qout => after_phase_i);

idownconv : DnConv_NCO port map(

nrst => nrst,

clk => clk8x,

omega => "01000000",

pass_r => after_phase_r,

pass_i => after_phase_i,

base_r => r,

base_i => i);

ipsf65T_r_rx : psf65T port map(

nrst => nrst,

clk => clk8x,

PSFin => r,

PSFout => rpsfout2);

ipsf65T_i_rx : psf65T port map(

nrst => nrst,

clk => clk8x,

PSFin => i,

PSFout => ipsfout2);

idnsam : DnSample

generic map(DnRatio => 8,

Dwidth => 10,

LatchTime => 1)

port map(

nrst => nrst,

upclk => clk8x,

dnclk => clk1x,

rdin => rpsfout2,

idin => ipsfout2,

rdout => rdnout,

idout => idnout);

rpsfout_final <= rnd(rdnout, 4);

ipsfout_final <= rnd(idnout, 4);

iqdemap : QAM16demapper

port map(

nrst => nrst,

sclk => clk1x,

rdata => rpsfout_final,

idata => ipsfout_final,

outbits => ri_after_demap);

ip2s : p2s

generic map(prate => 4)

port map(

nrst => nrst,

sclk => clk4x,

inbits => ri_after_demap,

outbit => p2sout);

mclkp : process

begin

mclk <= '1';

wait for 20 ns;

mclk <= '0';

wait for 20 ns;

end process;

rstp : process

begin

nrst <= '0';

wait for 100 ns;

nrst <= '1';

wait;

end process;

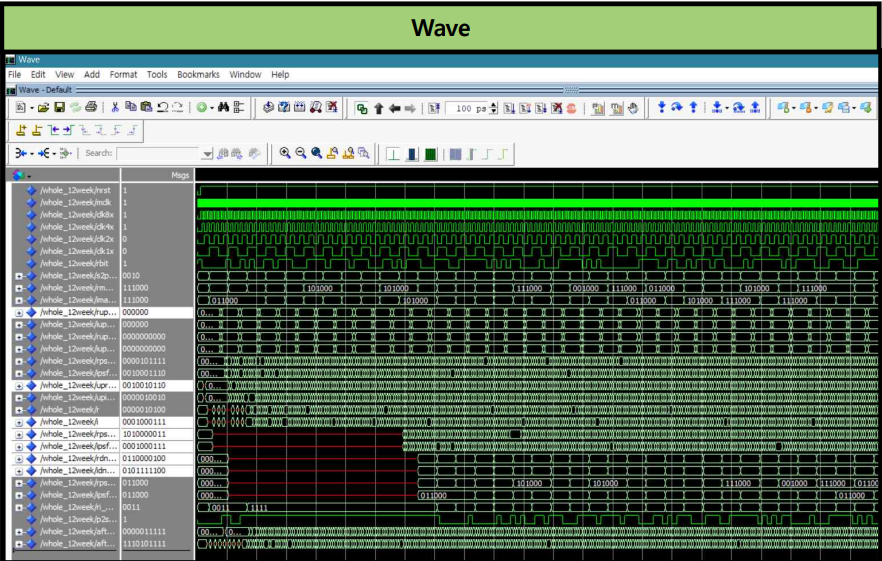

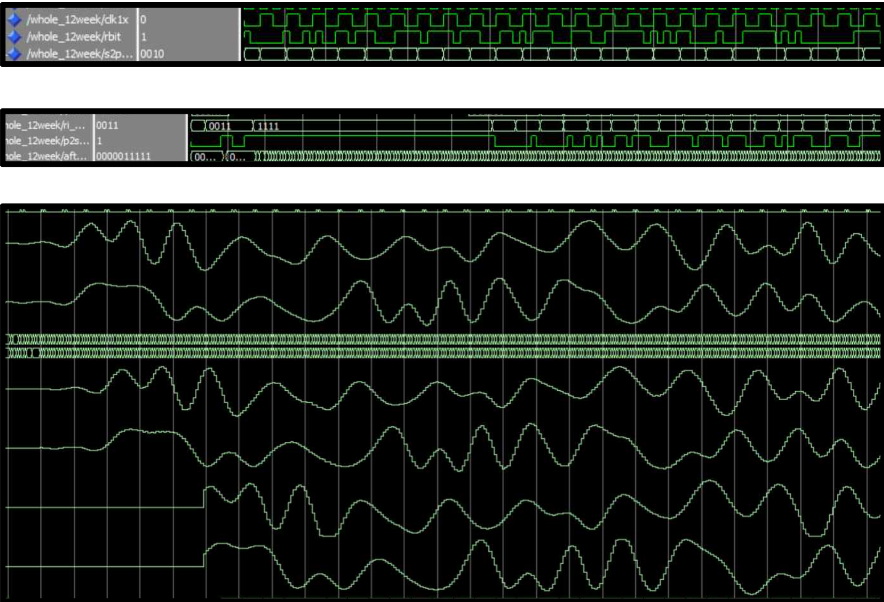

end behavior;Wave Capture

'Wireless Comm. > VHDL' 카테고리의 다른 글

| DQPSK DeMapper (0) | 2022.07.10 |

|---|---|

| DQPSK Mapper (0) | 2022.07.08 |

| Compare_PhaseSplit (0) | 2022.07.06 |

| PhaseSpitter (0) | 2022.07.05 |

| CPX_mul (0) | 2022.07.04 |

Comments