UOMOP

DQPSK Mapper 본문

RTL code

library ieee;

use ieee.std_logic_1164.all;

entity DQPSKmapper is

port(

nrst, clk : in std_logic;

cdata : in std_logic_vector(1 downto 0);

rout, iout: out std_logic_vector(5 downto 0));

end entity;

architecture arch of DQPSKmapper is

component QAM4mapper is

port(

nrst, sclk : in std_logic;

inbits : in std_logic_vector(1 downto 0);

rdata : out std_logic_vector(5 downto 0);

idata : out std_logic_vector(5 downto 0));

end component;

signal y, pdata : std_logic_vector(1 downto 0);

begin

process(cdata, pdata)

begin

if cdata = "00" then

y <= pdata;

elsif cdata = "01" then

if pdata = "00" then

y <= "01";

elsif pdata = "01" then

y <= "11";

elsif pdata = "10" then

y <= "00";

else

y <= "10";

end if;

elsif cdata = "10" then

if pdata = "00" then

y <= "10";

elsif pdata = "01" then

y <= "00";

elsif pdata = "10" then

y <= "11";

else

y <= "01";

end if;

else

if pdata = "00" then

y <= "11";

elsif pdata = "01" then

y <= "10";

elsif pdata = "10" then

y <= "01";

else

y <= "00";

end if;

end if;

end process;

process(nrst, clk)

begin

if nrst = '0' then

pdata <= "00";

elsif clk'event and clk = '1' then

pdata <= y;

end if;

end process;

iqpskmap : QAM4mapper

port map(

nrst => nrst,

sclk => clk,

inbits => y,

rdata => rout,

idata => iout);

end arch;TestBench code

library ieee;

use ieee.std_logic_1164.all;

entity tb_DQPSKmapper is

end entity;

architecture behavior of tb_DQPSKmapper is

component clkgen is

port(

nrst, mclk : in std_logic;

clk8x, clk4x, clk2x, clk1x : out std_logic);

end component;

component rbgen is

port(

nrst, clk : in std_logic;

rbit : out std_logic);

end component;

component s2p is

generic (prate : in integer);

port(

nrst, sclk, pclk, inbit : in std_logic;

outbits : out std_logic_vector((prate-1) downto 0));

end component;

component DQPSKmapper is

port(

nrst, clk : in std_logic;

cdata : in std_logic_vector(1 downto 0);

rout, iout: out std_logic_vector(5 downto 0));

end component;

signal nrst, mclk : std_logic;

signal clk8x, clk4x, clk2x, clk1x : std_logic;

signal rbit : std_logic;

signal s2pout : std_logic_vector(1 downto 0);

signal rmapout, imapout : std_logic_vector(5 downto 0);

begin

iclkgen : clkgen

port map(

nrst => nrst,

mclk => mclk,

clk8x => clk8x,

clk4x => clk4x,

clk2x => clk2x,

clk1x => clk1x);

irbgen : rbgen

port map(

nrst => nrst,

clk => clk4x,

rbit => rbit);

is2p : s2p

generic map(prate => 2)

port map(

nrst => nrst,

sclk => clk4x,

pclk => clk2x,

inbit => rbit,

outbits => s2pout);

idqpskmap : DQPSKmapper

port map(

nrst => nrst,

clk => clk2x,

cdata => s2pout,

rout => rmapout,

iout => imapout);

mclkp : process

begin

mclk <= '1';

wait for 20 ns;

mclk <= '0';

wait for 20 ns;

end process;

nrstp : process

begin

nrst <= '0';

wait for 100 ns;

nrst <= '1';

wait;

end process;

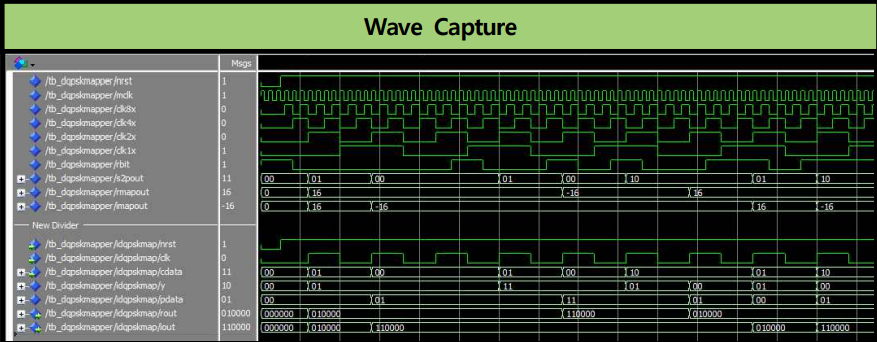

end behavior;Wave Capture

'Wireless Comm. > VHDL' 카테고리의 다른 글

| Whole Processing using DQPSK (0) | 2022.07.11 |

|---|---|

| DQPSK DeMapper (0) | 2022.07.10 |

| Whole Processing using PhaseSplitter (1) | 2022.07.07 |

| Compare_PhaseSplit (0) | 2022.07.06 |

| PhaseSpitter (0) | 2022.07.05 |

Comments