UOMOP

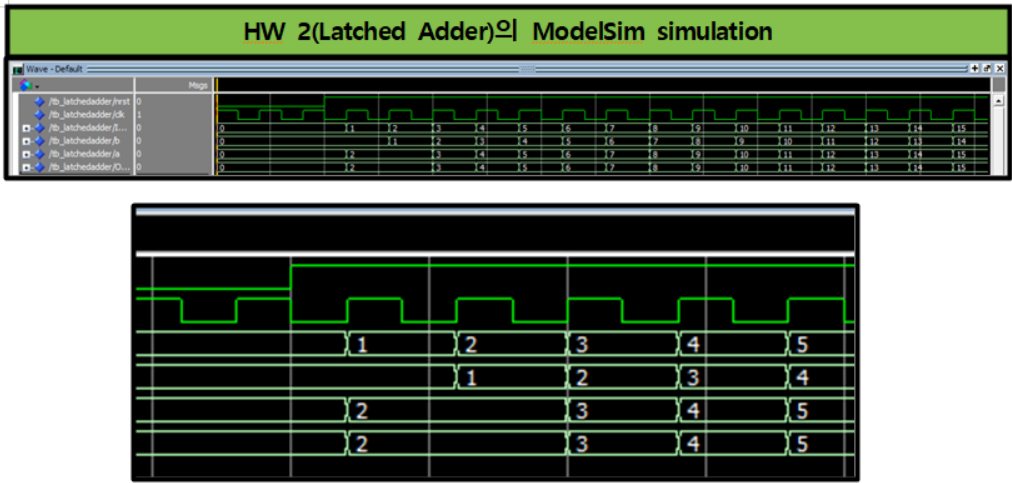

Latched Adder using VHDL 본문

Module Source Code

library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity latchedadder is

port(

nrst, clk : in std_logic;

InData : in std_logic_vector(7 downto 0);

OutData : out std_logic_vector(7 downto 0));

end latchedadder;

architecture behavior of latchedadder is

signal b, a : std_logic_vector(7 downto 0);

begin

process(nrst, clk)

begin

if nrst = '0' then

b <= (others => '0');

elsif clk = '1' and clk'event then

b <= InData;

end if;

end process;

process(nrst, clk)

begin

if nrst = '0' then

a <= (others => '0');

elsif clk = '1' and clk'event then

a <= b + "00000010";

end if;

end process;

OutData <= a;

end behavior;Testbench Source Code

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity tb_latchedadder is

end tb_latchedadder;

architecture behavior of tb_latchedadder is

component latchedadder

port (

nrst, clk : in std_logic;

InData : in std_logic_vector(7 downto 0);

OutData : out std_logic_vector(7 downto 0));

end component;

signal nrst, clk : std_logic;

signal InData8, OutData8, b, a : std_logic_vector(7 downto 0);

begin

ilatchedadder : latchedadder port map(

nrst => nrst,

clk => clk,

InData => InData8,

OutData => OutData8);

clkp : process

begin

clk <= '1';

wait for 20 ns;

clk <= '0';

wait for 20 ns;

end process;

rstp : process

begin

nrst <= '0';

wait for 100 ns;

nrst <= '1';

wait;

end process;

cnt8p : process(nrst, clk)

begin

if nrst = '0' then

InData8 <= (others => '0');

elsif clk = '1' and clk'event then

InData8 <= InData8 + '1';

end if;

end process;

b_go : process(nrst, clk)

begin

if nrst = '0' then

b <= (others => '0');

elsif clk = '1' and clk'event then

b <= InData8;

end if;

end process;

a_go : process(nrst, clk)

begin

if nrst = '0' then

a <= (others => '0');

elsif clk = '1' and clk'event then

a <= b + "00000010";

end if;

end process;

OutData8 <= a;

end behavior;

'Wireless Comm. > VHDL' 카테고리의 다른 글

| Serial to Parallel using VHDL (0) | 2022.04.26 |

|---|---|

| Parallel to Serial using VHDL (0) | 2022.04.26 |

| Clock Generator using VHDL (0) | 2022.03.22 |

| Random Bit Generator using VHDL (0) | 2022.03.22 |

| Up/Down 4bits counter using ModelSim (0) | 2022.03.22 |

Comments